FPGA build flows are at risk of compromise by internal or external adversaries. By modifying design and setting files of an EDA project, adversaries may insert Trojans, alter design operation, or leave the design more vulnerable to attack. It is therefore necessary for designers to verify and audit their FPGA build flows on-demand to ensure that their build flows and designs have not been altered.

The Enverite® EDA suite contains features that provide verification and auditing of FPGA build flows.

PV-Bit® Verification

PV-Bit® (Private Verification of FPGA Bitstreams) verification evaluates the equivalence of an FPGA bitstream and its physical netlist.

Trace® Archiver

Trace® archiver creates and verifies a tamper-evident auditable digital thread as a design traverses the build flow.

Retrace® Auditor

Retrace® auditor authenticates and verifies integrity of a Trace® digital thread and enables automated reproduction of the traced build.

Address your FPGA Build Flow Assurance Concerns

Functional Safety

Alteration to the design in the bitstream

Compromised IP

Trojan insertion

Compromised tooling or software

Attack during assembly and flash provisioning

Modification of 3PIP by an adversary

Modified design suites

Assurance EDA Suite for Security and Functional Safety

DO-254 / ED80 Airborne Electronic Hardware

ISO 26262 Road Vehicles Functional Safety

Nuclear Digital Instrumentation and Control

Rail & Transport Safety

Medical Product Safety

Defense Technologies

Enverite EDA features help you follow the latest high assurance guidelines

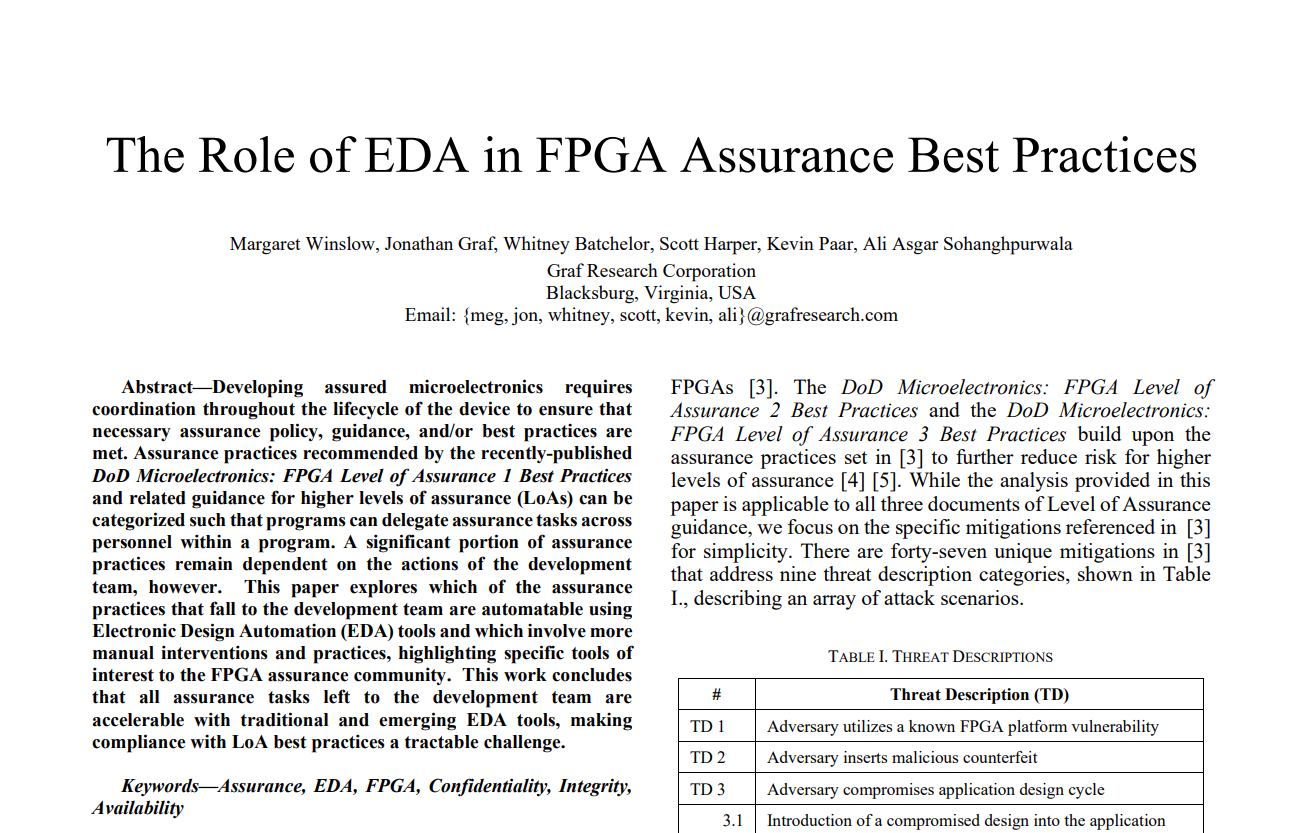

M. Winslow, J. Graf, W. Batchelor, S. Harper, K. Paar, A.A. Sohanghpurwala, “The Role of EDA in FPGA Assurance Best Practices,” GOMACTech 2024 Proceedings, March 2024.

The National Security Agency (NSA) released a series of reports on protecting and securing FPGAs “during manufacturing, acquisition, programming, and first attachment of the devices.” Many of the recommendations - including addressing the threats enumerated above - are uniquely achieved through the use of Enverite® EDA.

Check out “The Role of EDA in FPGA Assurance Best Practices” to see how Enverite® EDA and other high assurance EDA tools can help you accelerate the implementation of FPGA best practices.

More Information

Download our Enverite EDA suite overview here. Request further information on our products using the Request Documents form below.

Or, for sales inquiries, product demonstrations, and product support questions, contact us!